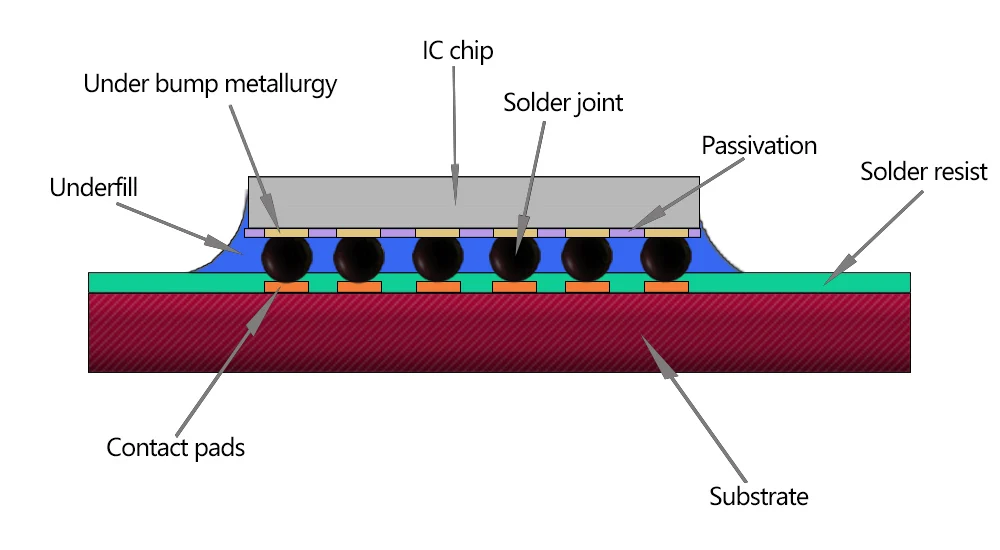

Underfill can properly protect the chips or semi-conductors from shock, drop, and vibration and helpfully reduces the strain on fragile soldering connections caused by the difference in thermal expansion between the silicon chip and its carrier (Two different materials).

It is a type of liquid polymer applied to the populated PCB (printed circuit board) after it has been subjected to the reflow process. Then it will be cured after placing the underfill. In this process the underfill encapsulates the bottom side of the silicon chip, filling the gap of the fragile interconnected pads between the chip’s bottom side and the PCB’s top side.

Why Underfill?

The primary purpose for considering the use of encapsulant underfill in electrical assembly is to reduce the impact of deviation in global thermal expansion characteristics between the silicon die and the underlying attached substrate. On conventional semi-conductors packaging, typically these stresses are absorbed by the natural flexibility of the wire leads. But, with direct-attach methods chips like solder ball arrays, the solder joints themselves dot represent the stress points in the structure and therefore are the most susceptible to stress failures. Unfortunately, these are also the most critical because a failure at any interconnect point would leads to the functionality failure of the circuit. By thoroughly filling into gaps between the chip, solder balls and PCB substrate, the underfill material can redistribute the strains and stresses from the coefficient of thermal expansion (CTE) mismatch and mechanical shock over the entire chip area.

Another benefits from underfilling is it’s production against moisture and other forms of contamination. But the negative factor raised up that the use of underfill increase the overall cost to the manufacturing operation and take difficult to rework. Therefore, most manufacturers perform a necessary functional test after reflow process and prior to the underfill operation.

When to Underfill

Because there are at least 50 different designs of CSP(chip scale package), plus a numbers of variables and operating conditions involved in interconnect design, it is difficult to provide a specific definition for when to use underfill. However, there are a myriad of key factors that should be taken into account when starting a PCB design. Including some of the critical factors:

Global Support behind Your Design and Manufacturing

When it comes to decide to use underfill technology to handle the chips package on electronics assembly, a range of challenges need to be taken into account to efficiently implement the process to achieve consistently reliable and durability results while maintaining required mass production throughput levels. Some of critical issues including: