Introduction: There are general discussions on the laminated structure of multi-layer printed circuit boards, and most PCB factories have relevant training about this knowledge, which have thoroughly and clearly explained various laminated stackup’s structures and principles.

In this article we are mostly focusing on discussing the advantage and it’s weakness of the common 4 layers PCB stack up. And, two crucial questions below will be answered:

Key words:

Stack-up (laminate structure): It means for layer sequence of copper layer and insulation dielectric sequence,correspondingly including it’s thickness such as:dielectric thickness,copper thickness.

Core(copper clad laminate): The skeleton of a printed circuit board,one double-sided copper clad PCB board, Usually it refers the double-sided panels that can be used as producing the PCB inner layers.

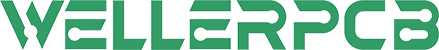

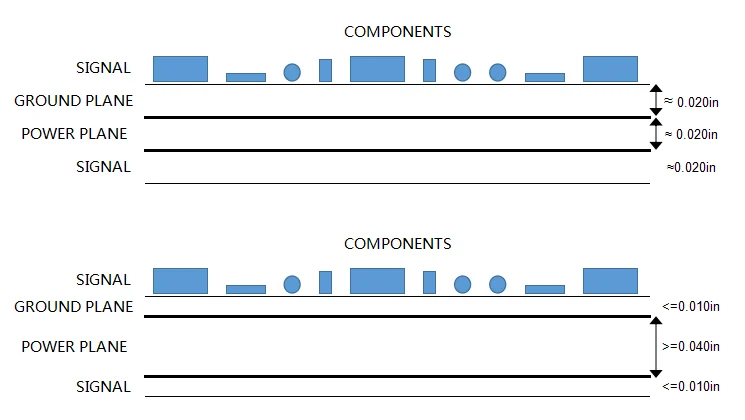

Figures 1 and 2 in below show two types of 4L PCB stack up. They have the same layer sequence as SIGNAL-GROUND-POWER-SIGNAL,but they have different thickness at it’s core. However,this small difference can greatly improve the PCB electronic working performance.

The generic Stack-up with power layer and ground planes layer

As shown in the above figure, both the top and bottom layer are the signal layers and both of them have a reference layer plane (one is ground layer and the other is power layer).The current can be returned via it’s adjacent reference layer, so as to reduce the current returning path’s loop area ,also reducing the inductance value of the current path. Low inductive current path can lower the interference of the noise and also minimized the signal radiation (no matter it is common mode or differential mode).

Generally speaking, the radiation intensity of a four-layer board is 20dB lower than that of a two-layer board with the same function. The key to minimize this is to keep the signal layer as mostly close to it’s reference layer as possible. Therefore, in order to furtherly improve the performance of Electromagnetic Compatibility (EMC) and lower the electromagnetic interference (EMI), it shall to minimize the dielectric thickness between signal layer and it’s reference shield layer. So,from the view of this technical point, the electronic performance in the stack up in fig 1 is weaker than stack up in fig 2 which have much less dielectric thickness so as generating a better compatible feature between signal layer and reference layer. But, this is not a serious flaw as these two type of stack up can meet the basic compatible demand. Here there is a note that these 2 types of stack up have same final thickness such as 62.00mil (0.062inch)

The weakness of above traditional 4L PCB stack-up

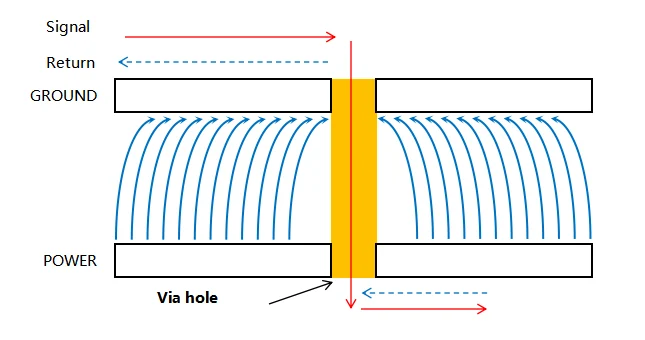

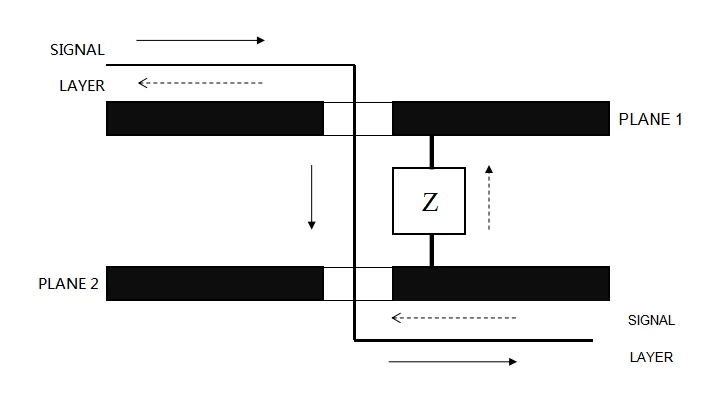

Firstly, the above stack up fig 1 and fig 2 will have problems once the signal track changed to layer4 from layer 1, refer below fig-3.

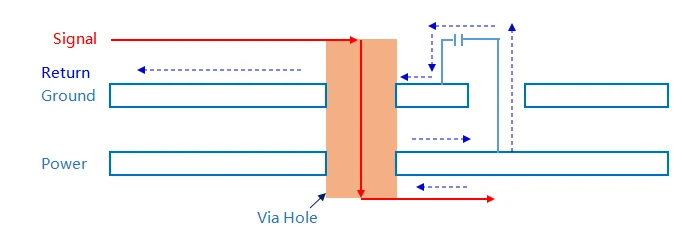

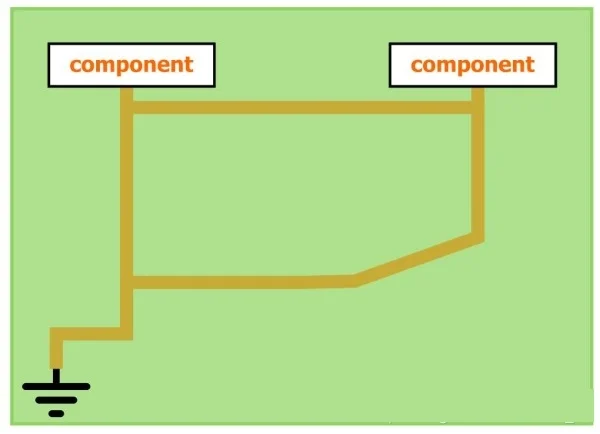

The red line stand for the signal current flow path, and the dotted blue line stand for the signal current returning path. If the signal frequency is enough high and the dielectric thickness between layers is enough thin, the returned current can smoothly go through the stacked layer’s capacitance barrier. And then bring the transforming from power layer to ground layer. But, as there is no direct connected path between power layer and ground layer,so there is an existing breaking node which can be treated as impedance, refer illustration as below fig-4.

If the stacked layer capacitance is not enough large, this relatively would lead to stacked layer impedance high.And then the current prefer to return from the low impedance zone, thereby this will increase the returning path area.correspondingly taking out radiation interference affecting other adjacent signals.

Reasonably that this situation should be avoided, but unfortunately, the stack up with final thickness 0.062 inch in fig 1 and fig 2 have poor stacked layer capacitance, so they will have a high impedance to ground plane. In this case, there may not take serious signal integrity problems, but EMI problems will certainly occur. This is why that it is necessary to avoid transforming the signal layer when using a stack up structured with power and ground planes, especially for high-speed clock signals.

Of course, if there is no way to avoid signal layer transforming, it would be necessary to place a decoupling capacitor at the zone of transformed layer, and mostly placed close to the through hole of the transformed layer, thereby lowering the impedance of the current returned path.

However, when the signal frequency is very high, the decoupling capacitor’s efficiency will be lost due to its own resonance. In general, to enable the decoupling capacitor to work, the signal frequency should not be higher than 200-300MHz.

After all, when the signal frequency is less than 200-300MHz, decoupling capacitors can be used to help layers transform;but it is necessary to raise up the stacked capacitance volume to avoid this issue for the higher frequency signals.

The above problems will not occur if the signal does not need to transform, but too less stacked layer capacitance will bring another serious issues: power transmission problems. Usually,most of ICs require extremely high transient currents, and when the rise time of the signal becomes smaller and smaller (the rise time of the signal is often related to the frequency, the smaller the time, the higher the frequency), the higher the frequency of the power supply. Commonly, the instantaneous power supply problem can be avoided by place the decoupling capacitor close to the IC, but if the high frequency of power supply is necessarily required,and higher than the resonant frequency of the decoupling capacitor itself, then the capacitor will transform to an inductance and lose the function of storing the power energy.

In today’s electronic field, more and more IC rise times are below 500ps, this raise up a challenge to the performance of decoupling capacitors. The layer stacked capacitance is a very preferable complement, which has a high enough resonant frequency to provide efficient instantaneous current. Thus, compared with general-purpose decoupling capacitors, layer stacked capacitors can be better to provide instantaneous power to high-speed ICs.

However, the method of reducing the thickness of the insulating layer to increase the layer stacked capacitance is sometimes not feasible because it will increase the cost.

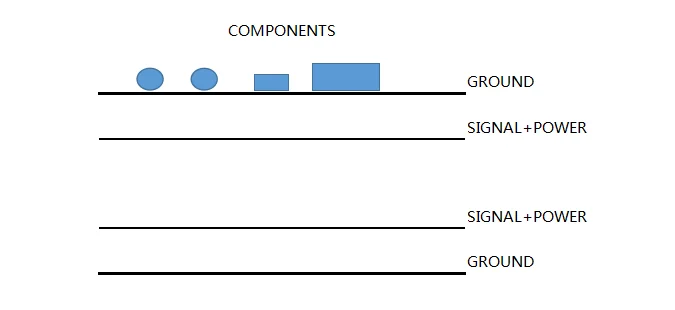

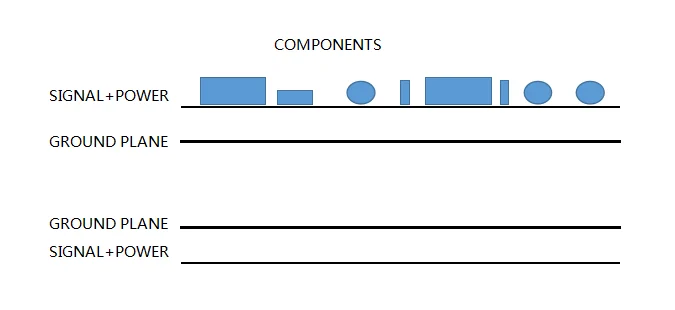

The stack up structure shown in figures 1 and 2, it is required the signal layer must have an adjacent reference layer, and the signal return path should be as small as possible. For these reasons, the stack-up shown in figure 6 is not an ideal stack-up because a large number of electronic components are placed on the surface, which break out the completeness of the ground plane. However, the third layer is a very good of current routing layer because it has the complete reference ground plane.

Both stack up in fig 6 and 7 have two ground plane layers, which provide a low impedance ground plane and help to reduce common mode radiation. At the same time, the ground plane of figure 6 wraps the signal layer to form a shield, which can be better to absorb most of the radiation interference from high-frequency signals. The two ground planes can be sufficiently connected by placing via holes, which will further generate a Faraday cage to suppress radiation. Of course, the stack up structure in figure 7 does not have this type of a shielding efficiency.

Neither of the above stack up has a complete power plane, therefore it have to transmit the power supply by placing copper plane or optimizing the electric net. If electronics components and signals can be complete placed on the first layer, the stack-up of figure 7 would be a highly recommended option because it has a complete ground plane. If not, the stack up structure of figure 6 can also be an alternative consideration.

Although there is no complete power plane, it can keep close to ground plane by place copper on power layer, that a large stacked layer capacitance can also be obtained to serve for high frequency signals. Some designers think that the decoupling effects via placing copper to power layer in figures 6 and 7 is more stronger than the decoupling effect of the Power and Ground planes from the traditional 4-layer stack up structure. Plus combining with common decoupling capacitors, better power performance can also be obtained.

Finally, in the stacked structure of figures 6 and 7, the high-speed signals can be layer transformed, because the reference of the signal has a complete reference ground plane (both sides), and the via holes placed between the ground planes provide good connectivity, so as to reduce the impedance of the current return path.

Copper pouring on top and bottom layer

In the above two types of improved stack up structures fig-6 & fig-7, the two middle layers in fig-7 are both GND planes. Except the power plane and signal track,whether it is necessary to pour extra copper, if yes, the poured copper should be connected to GND or Power layer?

First, the copper plane can play a role of shielding;

Whenever it is possible, pour the copper and connect it to ground.

Secondly, ground copper plane can avoid the formation of ground loops, of course,via through holes should be placed in appropriate places to connect the ground plane;

Also, ground copper plane can reduce the loop impedance of the signal, especially in double-layer boards.

Therefore, the 4L PCB board should be copper-poured as much as possible if allowed. So how to solve the problem of track impedance on the top-layer layout? Answer, 3W rules, keep the 3W distance between the ground and the impedance track, it can have less impact on the impedance, and generally 20mil spacing is sufficient.

Finally, as it is the foundation to the electronic circuit board so the designer need firstly to draw the PCB stack up before start a PCB layout design.