What is PCB Trace Impedance and How to Calculate it?

PCB trace impedance is the sum of all the resistance and reactance components of an electrical signal path. An ideal transmission line must have a characteristic impedance that matches both the transmitter and receiver of the intended signal. If the characteristic impedance of the matched transmission line is faithfully maintained, then the full signal sent by the transmitter is seen by the receiver at the end of the trace. There would be no reflection or attenuation of the signal. The full amount if signal power is absorbed by the receiver. For mismatched impedance, a reflection will occur at the far end and the complete signal will not be seen accurately at the receiver destination. Therefore, in practice, the details of the impedance control within the system need to be carefully considered.

For single-ended line transmission of an I/O signal, a 50 ohm impedance is often the required matching characteristic. The characteristic impedance of the signal path is a continuous 50 ohm path relative to the closest ground. The signal will return on the nearest ground path to the trace. Several applications have specific impedance requirements other than 50 ohms, based on legacy standards. Analog CATV video signals require a 75 ohm single-ended characteristic impedance, for example.

At higher frequencies, the PCB signal trace impedance will depend on the geometry of the circuit, so it has to be calculated. These calculations are complex. The impedance will depend on 4 parameters:

The impedance of traces is defined by more than only the size of the trace. When a trace is defined to require controlled impedance, the accuracy of the impedance itself is of higher importance than the geometry of the layout feature. In order to maintain the impedance accuracy, WELLER may change a trace width, trace height, or dielectric thickness given in the layout Gerber file. This will ensure that the final impedance is within the tolerance.

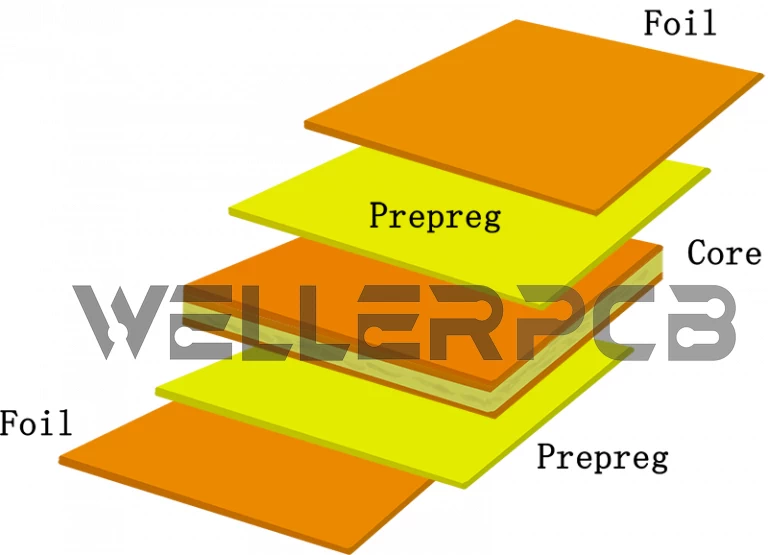

PCB Prepregs Materials

Prepregs are semi-cured materials used as bonding materials between two core laminates within a PCB. After the lamination step in the manufacturing process, the final thickness of the prepreg depends on the percentage of copper in adjoining conducting layers, the height of the copper, and the specific type of the prepreg used within the design.

Based Material Line Up S1000H (S1000HB)-PREPREG (B-STAGE)

| Glass style | RC (%) Nominal | Thickness | Dk | Df | |||||||

| mm | mil | 1GHz | 3GHz | 5GHz | 10GHz | 1 GHz | 3 GHz | 5 GHz | 10 GHz | ||

| 7628 | 43* | 0.185 | 7.28 | 4.81 | 4.74 | 4.74 | 4.73 | 0.014 | 0.015 | 0.015 | 0.016 |

| 7628 | 46 | 0.195 | 7.68 | 4.74 | 4.68 | 4.66 | 4.66 | 0.015 | 0.016 | 0.016 | 0.016 |

| 7628 | 48 | 0.205 | 8.07 | 4.70 | 4.63 | 4.61 | 4.61 | 0.015 | 0.016 | 0.016 | 0.017 |

| 7628 | 50 | 0.215 | 8.46 | 4.65 | 4.58 | 4.57 | 4.57 | 0.016 | 0.016 | 0.017 | 0.017 |

| 7628 | 52 | 0.225 | 8.86 | 4.59 | 4.52 | 4.51 | 4.50 | 0.016 | 0.016 | 0.017 | 0.017 |

| 1506 | 48 | 0.160 | 6.30 | 4.70 | 4.63 | 4.61 | 4.61 | 0.015 | 0.016 | 0.016 | 0.017 |

| 1506 | 50 | 0.170 | 6.69 | 4.65 | 4.58 | 4.57 | 4.57 | 0.016 | 0.016 | 0.017 | 0.017 |

| 1506 | 52 | 0.180 | 7.09 | 4.59 | 4.52 | 4.51 | 4.50 | 0.016 | 0.016 | 0.017 | 0.017 |

| 2116 | 52* | 0.113 | 4.45 | 4.59 | 4.52 | 4.51 | 4.50 | 0.016 | 0.016 | 0.017 | 0.017 |

| 2116 | 53* | 0.116 | 4.57 | 4.57 | 4.50 | 4.49 | 4.48 | 0.016 | 0.017 | 0.017 | 0.018 |

| 2116 | 55 | 0.120 | 4.72 | 4.53 | 4.45 | 4.43 | 4.43 | 0.017 | 0.017 | 0.018 | 0.018 |

| 2116 | 58 | 0.130 | 5.12 | 4.45 | 4.38 | 4.36 | 4.36 | 0.017 | 0.018 | 0.018 | 0.018 |

| 3313 | 57 | 0.100 | 3.94 | 4.48 | 4.41 | 4.39 | 4.39 | 0.017 | 0.018 | 0.018 | 0.018 |

| 1080 | 65 | 0.072 | 2.83 | 4.29 | 4.21 | 4.19 | 4.18 | 0.019 | 0.019 | 0.019 | 0.020 |

| 1080 | 68 | 0.081 | 3.19 | 4.21 | 4.13 | 4.11 | 4.11 | 0.020 | 0.019 | 0.020 | 0.020 |

| 1080 | 70 | 0.087 | 3.43 | 4.16 | 4.08 | 4.05 | 4.05 | 0.020 | 0.019 | 0.020 | 0.020 |

| 106 | 73 | 0.050 | 1.97 | 4.09 | 4.01 | 3.97 | 3.97 | 0.020 | 0.020 | 0.020 | 0.020 |

| 106 | 78 | 0.063 | 2.14 | 3.97 | 3.89 | 3.83 | 3.83 | 0.02 | 0.021 | 0.020 | 0.022 |

| Remark: | |||||||||||

| 1) Test by SPDR method. | |||||||||||

| 2) The data above show actual values and are not guaranteed, for your reference only. | |||||||||||

| 3) RC* is not common type for reference. | |||||||||||

| 4) Last update: Oct, 2020 | |||||||||||

Impedance-Control

During the lamination process, a high degree of process control and integrity must be maintained. Post-lamination thicknesses of prepregs are reasonably predictable. The resin content of the PCB material is important as the percentage of the resin content has a great impact on the final thickness. The higher the thickness of the dielectric material, the lower the dielectric constant of the PCB material will be.

High-speed materials have lower dielectric constants and are suitable for applications requiring transmission of high-speed signals, usually having signal frequencies above 500 MHz. A layout designer must include the impedance information in the fabrication drawing notes and tables. The information should include the impedance value, the trace width, the spacing for differential pairs and the layer on which the control impedance traces are routed.

How to Calculate the Impedance?

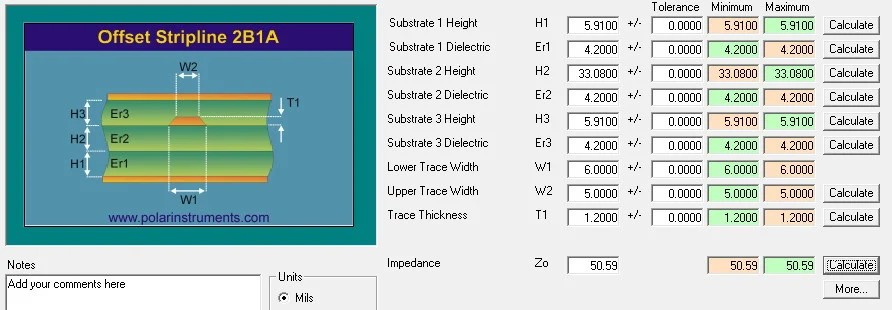

The calculation impedance software Polar Si9000 is popular in the PCB manufacture in present. Let me introduce it simply as below:

The width of the trace and height of the dielectric stack-up can be adjusted as needed in order to maintain the tolerance across a signal transmission line for +/- 10% of the ideal impedance value. Achieving this accuracy requires a good understanding of the Er values and experience about how dielectric laminates behave.

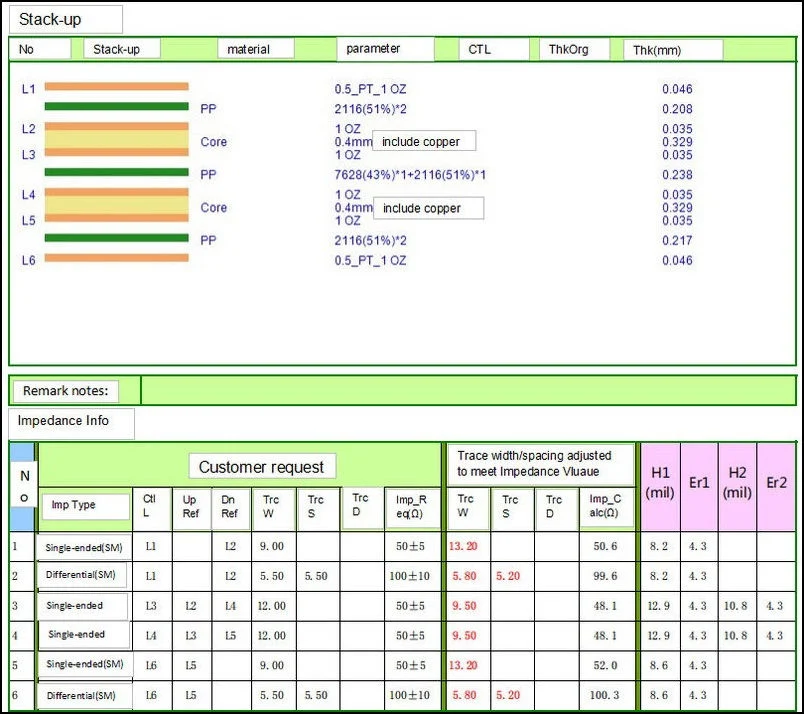

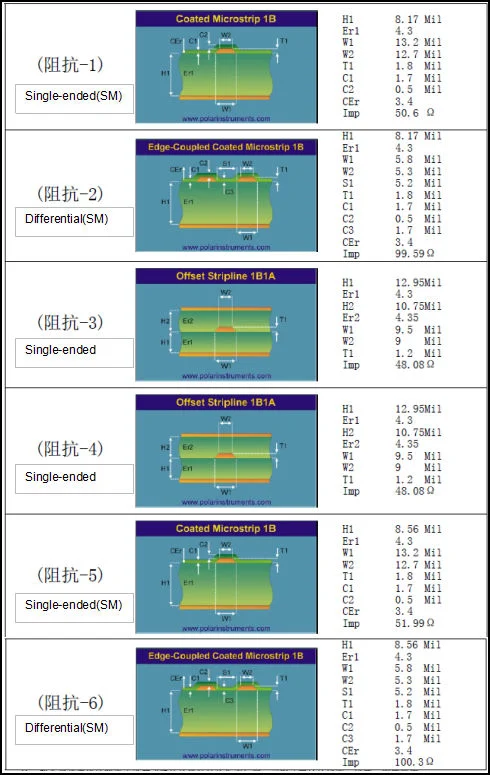

H1=> 8.17mil is the PP thickness between impedance trace layer and reference layer,it is 0.208mm per stackup at here.

Er1=>4.3 is the base material PP’s dielectric constant

W1=>13.2mil is the calculation trace width(the adjusted trace width,need to adjust trace width to meet impedance)

W2=>12.7mil is the upper trace width, after etching the trace will be like a Trapezoid,this determined by the copper thickness(trace thickness)

T1=>1.8mil is final nominal copper thickness

C1=>1.7mil is nominal S/M thickness

C2=>0.5mil is nominal S/M thickness on trace corner

CEr=>is S/M’ dielectric constant

Imp 50.6Ω=> is the impedance calculated theoretical

When the material is specified by PCB designer, the Er value is fixed. usually the normal FR4 Er value is about 4.1–4.7. The Er bigger the impedance value will smaller.

If there is no stack-up required in the PCB manufacturing specification file, we can design a stack-up (adjust the H1, inner layers is H1,H2) to meet impedance value. but sometimes there are many groups impedance in same layers, due to Er and H1(H2) have fixed, we need to adjust trace width(spacing) to meet all of the impedance value, otherwise, some groups impedance value can’t be meet.

If customer provide the stackup, The H1(H2) have been fixed, if the impedance calculation can’t meet the required value, then we will suggest to change the trace width(spacing) or to change H1(H2) PP thickness to ensure impedance vlue.

Sometimes the impedance trace width have been specified in specification of PCB FAB drawing, but can’t search the trace from gerber, or some impedance trace in gerber have no reference layer(or lots of the parts have no reference), such trace can’t meet impedance.

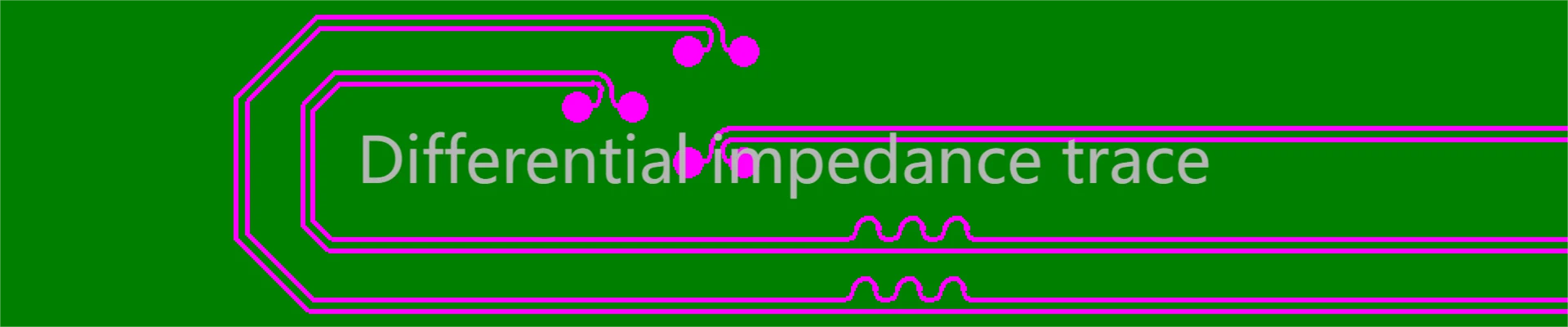

For the differential pair impedance trace, If the parallel lines spacing not fix, the actually value of them will exist distortion(some part the impedance value will out of tolerance).

Usually all of the impedance trace sample will be an impedance test coupon added. In coupon the differential pair trace spacing is completely same, when the value on test coupon are ok, there will be considered the impedance have been controlled OK.

If you have any question on trace impdeance before you design a comlex PCB board, you can contact us by service@wellerpcb.com